Port Declaration

모듈을 설명하기 앞서서 기본적인 내용인 포트에 대해서 설명하려고 한다.

지난시간에도 설명하였지만, 모듈의 입출력 타입은 3가지가 존재한다.

input: input ports

output: output ports

inout: bidirectional ports

(필자는 용역을 여러번 해봤지만, 아직까지 inout을 써보지 못했다.)

input의 경우 외부에서 들어오는 형태는 상관이 없지만, 내부에서는 net(wire)타입이여야 한다.

inout의 경우 외부에서 net타입으로 들어와야하고 모듈 내부에서도 net타입이여야 한다.

output의 경우 내부에서는 reg나 net 상관없지만 외부에서는 net으로 받아야 한다.

기본적으로 변수들은 wire로 설정되는데 출력단에서 값을 유지하기 위해서는 기억소자인 reg를 사용해야 한다.

wire의 경우 전선이고 단순하게 값을 연결만 해주는 것으로 생각하면 된다.

Port Connection Rules

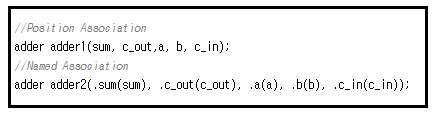

각각의 모듈(Component)을 가져오는(Instantiation) 방법에는 2가지가 존재한다.

Positional Association: 내연적인(Implicit) 방법으로 각 변수들의 위치에 따라서 연결하는 방법이다.

Named Association: 외연적인(Explicit) 방법으로 이름에 따라서 연결하는 방법이다.

앞 시간에 배운 adder를 예를 들어 설명하면

adder 모듈에는 sum, c_out, a, b, c_in 5개의 변수가 존재하는데

순서대로 변수를 넣을 경우 Positional Association이고 이름에 따라서 넣을 경우 Named Association이다.

Module

모듈은 특정한 기능을 하는 프로그램으로 생각해도 좋고 프로그래밍에서의 함수와 비슷한 개념이다.

베릴로그에는 함수(function)과 테스트(task)와 서브모듈(submodule)이 존재하므로

실제로는 함수, 테스크, 서브모듈 -> 모듈 -> 프로그램(FPGA)라고 생각하면 된다.

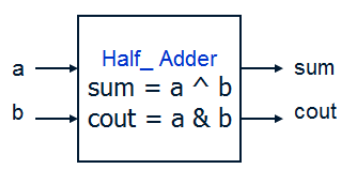

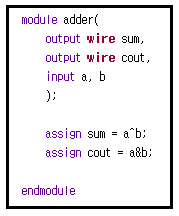

위 그림과 같이 Half Adder 모듈을 만들어 보도록 하겠다.

모든 변수의 경우 wire타입으로 구성되어 있고 수식에 맞게 출력 값에 입력 값을 연산하여 대입해주었다.

위 모듈이 맞게 동작하는지 확인하는 방법으로는 테스트벤치를 이용하여 시뮬레이션 하는 방법이 있다.

다음시간에는 테스트벤치를 이용하여 모듈을 테스트하는 방법에 대해서 소개하고

이후에는 베릴로그에서 모델링하는 방법 3가지에 대해서 설명하도록 하겠다.

순서: Testbench-> Structural Modeling -> Dataflow Modeling -> Behavioral Modeling

'Hardware > FPGA' 카테고리의 다른 글

| [Verilog] #3-1 Structural Modeling (Gate level Modeling) (0) | 2020.12.09 |

|---|---|

| [Verilog] #2 테스트벤치 (Testbench) (1) | 2020.12.07 |

| [Verilog] #0 베릴로그(Verilog)란? / 데이터 타입(Data Types) (0) | 2020.12.07 |